US006967347B2

# (12) United States Patent

Estes et al.

### (10) Patent No.: US 6,967,347 B2

(45) **Date of Patent:** \*Nov. 22, 2005

# (54) TERAHERTZ INTERCONNECT SYSTEM AND APPLICATIONS

(75) Inventors: Michael J. Estes, Longmont, CO (US); Garret Moddel, Boulder, CO (US)

(73) Assignee: The Regents of the University of Colorado, Boulder, CO (US)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

This patent is subject to a terminal disclaimer.

(21) Appl. No.: 10/462,491

(22) Filed: Jun. 14, 2003

#### (65) **Prior Publication Data**

US 2004/0069984 A1 Apr. 15, 2004

#### Related U.S. Application Data

(63) Continuation-in-part of application No. 10/337,427, filed on Jan. 6, 2003, and a continuation-in-part of application No. 10/140,535, filed on May 6, 2002, and a continuation-in-part of application No. 10/103, 054, filed on Mar. 20, 2002, now abandoned, and a continuation-in-part of application No. 09/860,972, filed on May 21, 2001, now Pat. No. 6,563,185, which is a continuation-in-part of application No. 09/860, 988, filed on May 21, 2001, now Pat. No. 6,534,784.

| (51) | Int. Cl. <sup>7</sup> | H01L 31/3           | 336 |

|------|-----------------------|---------------------|-----|

| (52) | U.S. Cl               | <b>257/25</b> ; 257 | /30 |

| (58) | Field of Search       | 257/25, 30,         | 31, |

|      |                       | 257/32 34 35 36     | 46  |

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

| 5,056,111 A * | 10/1991 | Duling et al 375/259     |

|---------------|---------|--------------------------|

| 5,093,692 A * | 3/1992  | Su et al 257/104         |

| 5,287,212 A * | 2/1994  | Cox et al 398/183        |

| 5,754,948 A * | 5/1998  | Metze 455/41.2           |

| 5,825,240 A * | 10/1998 | Geis et al 327/570       |

| 5,895,934 A * | 4/1999  | Harvey et al 257/49      |

| 6,049,308 A * | 4/2000  | Hietala et al 343/700 MS |

| 6,664,562 B2* | 12/2003 | Weiss et al 257/21       |

<sup>\*</sup> cited by examiner

Primary Examiner—David Nelms

Assistant Examiner—Thinh T. Nguyen

(74) Attorney, Agent, or Firm—Michael Pritekau; Yoriko

Morita

#### (57) ABSTRACT

An assembly includes a first electrical circuitry for providing a first electrical signal containing data and a transmitting arrangement, connected with the first electrical circuitry, for receiving the first electrical signal and for converting the first electrical signal into an electromagnetic signal containing at least a portion of the data. The electromagnetic signal has a carrier frequency greater than 300 GHz. The assembly also includes a receiving arrangement for receiving the electromagnetic signal and for converting the electromagnetic signal into a second electrical signal containing at least some of the portion of the data, and a second electrical circuitry connected with the receiving arrangement and configured for receiving the second electrical signal.

#### 53 Claims, 29 Drawing Sheets

60B 54 16B 50 14 52 12 <u>13</u>

FIG. 1B

FIG. 1C

FIG. 1D

FIG. 2A

FIG. 2B

FIG. 3B

FIG. 4B

FIG. 4C

FIG. 4D

FIG. 5

FIG. 6B

FIG. 6D

FIG. 6E

FIG. 7B

FIG. 7C

FIG. 7D

FIG. 8C

FIG. 9C

\*Nov. 22, 2005

FIG. 10

FIG. 11

FIG. 14C

**Patent**

\*Nov. 22, 2005

**Sheet 25 of 29**

US 6,967,347 B2

**FIG. 15A**

FIG. 15B

FIG. 15C

#### TERAHERTZ INTERCONNECT SYSTEM AND APPLICATIONS

#### RELATED APPLICATION

The present application is a Continuation-in-Part of U.S. patent application Ser. No. 10/337,427, filed Jan. 6, 2003 entitled OPTICAL INTERCONNECTS FOR USE WITH HIGH SPEED ELECTRON TUNNELING DEVICES, which in turn is a Continuation-in-Part of U.S. patent 10 application Ser. No. 09/860,988 now U.S. Pat. No. 6,534, 784 entitled METAL-OXIDE ELECTRON TUNNELING DEVICE FOR SOLAR ENERGY CONVERSION filed on May 21, 2001, Ser. No. 09/860,972 now U.S. Pat. No. 6,563,185 entitled HIGH SPEED ELECTRON TUNNEL- 15 ING DEVICE AND APPLICATIONS filed on May 21, 2001, Ser. No. 10/103,054 entitled SURFACE PLASMON DEVICES filed on Mar. 20, 2002, now abandoned and Ser. No. 10/140,535 entitled SURFACE PLASMON DEVICES filed May 6, 2002. All of the aforementioned patent appli- 20 cations and patents are incorporated herein by reference in their entirety.

#### BACKGROUND OF THE INVENTION

The present invention relates generally to electronic devices. More particularly, the present invention relates to interconnection of electronic devices at carrier frequencies in a range from a few gigahertz to several hundreds of terahertz, and more specifically to terahertz interconnection 30 of electronic devices.

Increased amounts and speed of data transfer in communication and computing systems pose a challenge to the current state of device technology. Large quantities of information must be transferred quickly across distances ranging 35 from very short distances, from between chips as well as between boards containing chips, to longer distances between racks of devices, very short reach (VSR)/optical Ethernet and beyond. Even with the development of highspeed communications switches and routers, the data must 40 be taken in and out of such high-speed devices at compatibly high rates in order for the entire system to function efficiently.

Radio frequency (RF) inter-chip and intra-chip connections have been developed as a possible way of transferring 45 data within and between chips. However, RF interconnects use large antennae and/or waveguides on or connected to chips, thus requiring valuable on-clip and device "real estate." RF interconnects are limited in data transfer speed due to the use of radio frequencies. Furthermore, It is 50 submitted that the design and manufacture of such RF lines for high signal frequencies is an expensive part of prior art RF interconnection design.

Other researchers have suggested the use of optical signals as an alternative to electrical signals in providing inter- 55 Regarding the "standard I.E.E.E. definition of 'millimeterand intra-chip connections. For instance, parallel fiber-optic interconnects which are edge-connected to semiconductor devices have been developed for use within systems with a large number of electronic components (e.g., computers).<sup>2</sup> Although optical interconnect technology promises the pos- 60 sibility of higher rate data transfer than electrical interconnects, optical interconnect technology, as heretofore suggested, is still cost prohibitive in comparison. There is potentially a huge market for high speed interconnect arrangements because all desktop computers and local area 65 networks would benefit from the use of high speed interconnects between components on chips, between chips, etc.

Currently, electrical interconnects are generally used in communication and computing systems for power and data signal distribution, such as in bus lines, etc. Electrical interconnects, however, require hardwired connections such as, for example, lithographed lead lines on a chip, wire bonds from the chip to a chip package, pins leading from inside the package to a circuit board, printed circuit board wiring, edge connectors from circuit board to other boards, input/output (I/O) devices, data storage devices, and others. Such hardwired connections add parasitic capacitance, inductance, and resistance, which seriously degrade data transmission at high data bandwidths. Thus, the cost and performance limitations of electrical interconnects are compounded as circuits are made to operate at increasingly high frequencies. At high frequencies, electrical interconnects are limited in connection distance and require large amounts of power as well as signal reconditioning. Applicants submit that there are at least two issues contributing to this problem. First issue is the relative change in material properties, such as refractive index and electromagnetic radiation propagation speed, over the bandwidth of the signal. A second, and perhaps more significant, issue is the relative difference in wavelength over the bandwidth of the signal. For example, if the signal bandwidth is centered at zero frequency (i.e., DC), then the wavelength of different signal components may range from infinity (for the DC components) to, for instance, centimeters for components at tens of gigahertz. This enormous range in wavelength makes it difficult to design electrical transmission paths which will work efficiently over the entire bandwidth range.

In addition to the aforementioned RF inter- and intra-chip interconnects, other wireless interconnects at other frequencies have also been suggested. For example, wireless data communications link between circuit components using GaAs-based MIMIC transmit/receive integrated circuit devices, operating at high-bandwidth millimeter-wave frequencies, coupled to corresponding circuit components, such as digital processing units (or CPUs) have been disclosed by Metze in U.S. Pat. No. 5,754,948 (hereinafter, Metze). It is submitted, however, that GaAs-based MIMICs are complex devices which require expensive epitaxial growth techniques in the fabrication. Applicants submit that epitaxial growth techniques are expensive and severely limit the integration of devices with different epitaxial layer structures. Also, the disclosure of Metze is confined to millimeter-wave frequencies; specifically, the transmit/receive circuit of Metze is described as preferably operating:

at frequency ranges above 35 GHz, and most preferably at frequencies between 60 GHz and 94 GHz . . . other frequencies may be utilized and still fall within the standard I.E.E.E. definition of "millimeter-wave" for purposes of this invention. (Metze, column 5 lines 25-32)

wave" as referred to by Metze, according to the IEEE Virtual Museum website, the millimeter wave region is generally considered to correspond to 30 GHz to 300 GHz.<sup>3</sup>

As another example of wireless interconnects, in U.S. Pat. No. 5,056,111, Duling, III, et al. (hereinafter Duling) discloses a communication system for transmitting and receiving terahertz signals, which involves the generation of sub-picosecond (i.e., terahertz) pulses for transmission of data. However, Applicants submit that ultrashort pulse generation, such as that disclosed in Duling, require complex systems such as femtosecond lasers that are impractical to use as a replacement for local electrical interconnects. As

3

will be described at appropriate points below, the present invention recognizes certain problems with both the electrical interconnects and wireless interconnection schemes which are thought to be unresolved by the prior art.

As will be seen hereinafter, the present invention provides 5 a significant improvement over the prior art as discussed above by virtue of its ability to provide the increased performance while, at the same time, having significant advantages in its manufacturability. This assertion is true for electromagnetic devices generally, which take advantage of 10 the present invention, as well as data communication and computing devices in particular.

#### SUMMARY OF THE INVENTION

As will be described in more detail hereinafter, there is disclosed herein an integrated circuit chip including a formation of integrated layers. The integrated layers are configured so as to define at least one integrated electronic component as well as an integrated electron tunneling 20 device. The integrated electron tunneling device includes first and second non-insulating layers spaced apart from one another such that a given voltage can be provided across the first and second non-insulating layers. The integrated electron tunneling device further includes an arrangement dis- 25 posed between the first and second non-insulating layers and configured to serve as a transport of electrons between and to the first and second non-insulating layers. The arrangement includes at least a first layer configured such that the transport of electrons includes, at least in part, transport by 30 means of tunneling. The integrated electron tunneling device further includes an antenna structure connected with the first and second non-insulating layers, and the integrated electron tunneling device is electrically connected with the integrated electronic component.

In one aspect of the invention, a method for fabricating an integrated circuit chip is disclosed. The method includes forming a plurality of integrated layers, where the forming step includes the steps of defining at least one integrated electronic component and defining an integrated electron 40 tunneling device. The integrated electron tunneling device includes first and second non-insulating layers spaced apart from one another such that a given voltage can be provided across the first and second non-insulating layers. The integrated electron tunneling device further includes an arrange- 45 ment disposed between the first and second non-insulating layers and configured to serve as a transport of electrons between and to the first and second non-insulating layers. The arrangement includes at least a first layer configured such that the transport of electrons includes, at least in part, 50 transport by means of tunneling. The integrated electron tunneling device further includes an antenna structure connected with the first and second non-insulating layers. The method further includes electrically connecting the integrated electron tunneling device with the integrated elec- 55 tronic component.

In another aspect of the invention, an integrated circuit chip includes a formation of integrated layers, which integrated layers are configured so as to define at least one integrated electronic component. The integrated circuit chip 60 also includes an electron tunneling device including first and second non-insulating layers spaced apart from one another such that a given voltage can be provided across the first and second non-insulating layers. The electron tunneling device further includes an arrangement disposed between the first and second non-insulating layers and configured to serve as a transport of electrons between and to the first and second

4

non-insulating layers. The arrangement includes at least a first layer configured such that the transport of electrons includes, at least in part, transport by means of tunneling. The electron tunneling device further includes an antenna structure connected with the first and second non-insulating layers, and the electron tunneling device is formned on top of and separately from the formation of integrated layers without interference with an intended function of the integrated electronic component and its spatial location while being electrically connected with the integrated electronic component.

In still another aspect of the invention, an integrated circuit chip includes a formation of integrated layers, which formation of integrated layers is configured to define at least one integrated electronic component and is further configured to define an integrated optoelectronic device having an antenna. The antenna is configured to receive an optical signal. The integrated optoelectronic device is electrically connected with the integrated electronic component.

In yet another aspect of the invention, an integrated circuit chip includes a formation of integrated layers defining at least one integrated electronic component. The integrated circuit chip also includes an optoelectronic device having an antenna, which antenna is configured to receive an optical signal incident thereon. The optoelectronic device is formed on top of and separately from the formation of integrated layers without interference with an intended function of the integrated electronic component and its spatial location while being electrically connected with the integrated electronic component. In an alternative embodiment, the optoelectronic device is configured to provide an optical signal while the antenna is configured instead to transmit the optical signal.

In a further aspect of the invention, an integrated circuit 35 chip includes at least one substrate and circuitry formed on the substrate, which circuitry includes at least first and second integrated electronic components. The integrated circuit chip also includes a first optoelectronic device for providing an optical signal. The first optoelectronic device includes a first antenna, which first antenna is configured to emit the optical signal, and the first optoelectronic device is supported on the substrate while being electrically connected with the first integrated electronic component. The integrated circuit chip further includes a second optoelectronic device. The second optoelectronic device includes a second antenna, which second antenna is configured to receive the optical signal from the first antenna such that first and second optoelectronic devices are in optical communication with one another, while the second optoelectronic device is also supported on the substrate and is electrically connected with the second integrated electronic component.

In a still further aspect of the invention, an integrated circuit assembly includes first and second substrates. First circuitry, including at least a first integrated electronic component, is formed on the first substrate, and second circuitry, including at least a second integrated electronic component, is formed on the second substrate. The integrated circuit assembly also includes a first optoelectronic device for providing an optical signal. The first optoelectronic device includes a first antenna, which is configured to emit the optical signal, and is supported on the first substrate while being electrically connected with the first integrated electronic component. The integrated circuit assembly further includes a second optoelectronic device including a second antenna. The second optoelectronic device is supported on the second substrate and is electrically connected with the second integrated electronic component. The sec5

ond antenna is configured to receive the optical signal from the first antenna such that the first and second optoelectronic devices are in optical communication with one another.

In another aspect of the invention, an assembly includes an optoelectronic system, in which an optical signal is 5 present and which includes at least one optoelectronic device configured to act on the optical signal. The assembly also includes an electron tunneling device also configured to act on the optical signal. The electron tunneling device includes first and second non-insulating layers, which are 10 spaced apart from one another such that a given voltage can be provided across the first and second non-insulating layers, and an arrangement disposed between the first and second non-insulating layers, which arrangement is configured serve as a transport of electrons between and to the first 15 and second non-insulating layers. The arrangement includes a first amorphous layer configured such that using only the first amorphous layer in the arrangement would result in a given value of nonlinearity in the transport of electrons, with respect to the given voltage. The arrangement also includes 20 a different, second layer disposed directly adjacent to and configured to cooperate with the first amorphous layer such that the transport of electrons includes, at least in part, transport by means of tunneling through the first amorphous layer and the second layer, and such that the nonlinearity, 25 with respect to the given voltage, is increased over and above the given value of nonlinearity by the inclusion of the second layer without the necessity for any additional layer. The assembly further includes an optical configuration cooperating with the electron tunneling device and with the 30 optoelectronic device such that the optical signal is transmitted therebetween.

In a still another aspect of the invention, a device includes a waveguide, which waveguide in turn includes an optical input port. The optical input port is configured for receiving 35 an input light. The waveguide also includes an optical output port and is configured for directing the input light from the optical input port toward the optical output port. The device also includes an optoelectronic assembly, which includes an electron tunneling device. The electron tunneling device 40 includes first and second non-insulating layers, which are spaced apart from one another such that a given voltage can be provided thereacross, and an arrangement disposed between the first and second non-insulating layers and configured to serve as a transport of electrons between and 45 to the first and second non-insulating layers. The arrangement includes at least a first layer configured such that the transport of electrons includes, at least in part, transport by means of tunneling. The optoelectronic assembly also includes a coupling arrangement configured to cooperate 50 with the electron tunneling device and the waveguide for coupling at least a portion of the input light from the waveguide into the electron tunneling device.

In yet another aspect of the invention, an arrangement includes an optical waveguide with an optical input port, 55 which optical input port is configured for receiving an input light, and an optical output port. The optical waveguide is configured for directing the input light from the optical input port toward the optical output port. The arrangement further includes an optoelectronic assembly with a surface plasmon 60 device, which is configured to act on an input signal. The surface plasmon device includes a device input port, which is configured to receive the input signal, a device output port and a structure including a tunneling junction connected with the device input port and the device output port. The 65 tunnelinig junction is configured in a way (i) which provides electrons in a particular energy state within the structure, (ii)

6

which produces surface plasmons in response to the input signal, (iii) which causes the structure to act as a surface plasmon waveguide for directing at least a portion of the surface plasmons along a predetermined path toward the device output port such that the surface plasmons so directed interact with the electrons in a particular way, and (iv) which produces at the device output port an output signal resulting from the particular interaction between the electrons and the surface plasmons. The optoelectronic assembly further includes a coupling arrangement, which is configured to cooperate with the surface plasmon device and the optical waveguide for coupling at least a portion of the input light from the waveguide into the surface plasmon device as the input signal.

In a further aspect of the invention, an integrated circuit chip includes a substrate and a formation of integrated layers supported on the substrate, which integrated layers are configured so as to define at least one integrated electronic component. The integrated circuit chip also includes an optical waveguide, which is also supported on the substrate and includes an optical input port configured for receiving an input light including a clock signal encoded thereon. The integrated circuit chip further includes at least one optoelectronic assembly electrically connected with the integrated electronic component and including an electron tunneling device. The electron tunneling device includes first and second non-insulating layers spaced apart from one another such that a given voltage can be provided thereacross. The electron tunneling device also includes an arrangement disposed between the first and second non-insulating layers and configured to serve as a transport of electrons between and to the first and second non-insulting layers. The arrangement includes at least a first layer configured such that the transport of electrons includes, at least in part, transport by means of tunneling. The optoelectronic assembly also includes a coupling arrangement configured to cooperate with the electron tunneling device and the optical waveguide for coupling at least a portion of the input light including the clock signal from the waveguide into the electron tunneling device. The electron tunneling device is configured to (i) receive the portion of the input light, (ii) produce an electric signal and (iii) transmit the electric signal toward the integrated electronic component electrically connected with the optoelectronic assembly for use by the integrated electronic component.

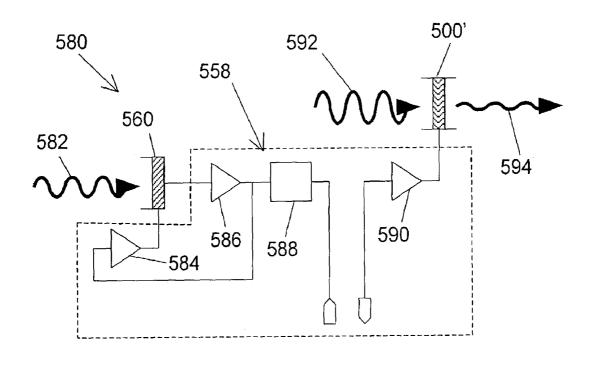

In another aspect of the invention, an assembly includes a first electrical circuitry for providing a first electrical signal containing data. A transmitting arrangement is connected with the first electrical circuitry and is configured for receiving the first electrical signal and for converting the first electrical signal into an electromagnetic signal containing at least a portion of the data. The electromagnetic signal has a carrier frequency greater than 300 GHz. The assembly further includes a receiving arrangement configured for receiving the electromagnetic signal and for converting the electromagnetic signal into a second electrical signal containing at least some of the portion of the data, and a second electrical circuitry connected with the receiving arrangement and configured for receiving the second electrical signal.

In still another aspect of the invention, a method for use in an assembly including at least a first electrical circuitry for providing a first electrical signal containing data and a second electrical circuitry for receiving a second electrical signal is disclosed. The method includes connecting the first electrical circuitry with a transmitting arrangement configured for receiving the first electrical signal and for convert-

ing the first electrical signal into an electromagnetic signal containing at least a portion of the data. The electromagnetic signal has a carrier frequency greater than 300 GHz. The method further includes connecting the second electrical circuitry with a receiving arrangement configured for receiv- 5 ing the electromagnetic signal and converting the electromagnetic signal into the second electrical signal containing at least some of the portion of data to be received by the second electrical circuitry.

In yet another aspect of the invention, another method for 10 use in an assembly including at least a first electrical circuitry for providing a first electrical signal containing data and a second electrical circuitry for receiving a second electrical signal is disclosed. The method includes, at a first location, receiving the first electrical signal from the first 15 electrical circuitry, and converting the first electrical signal into an electromagnetic signal containing at least a portion of the data. The electromagnetic signal has a carrier frequency greater than 300 GHz. The method further includes, at a second location, receiving the electromagnetic signal, 20 converting the electromagnetic signal into the second electrical signal containing at least some of the portion of the data, and directing the second electrical signal to the second electrical circuitry.

In a further aspect of the invention, an assembly includes 25 a first electrical circuitry for providing a first electrical signal containing data, and a transmitting arrangement connected with the first electrical circuitry and configured for receiving the first electrical signal and for converting the first electrical signal into an electromagnetic signal containing at least a 30 portion of the data. The assembly further includes a receiving arrangement for receiving the electromagnetic signal and for converting the electromagnetic signal into a second electrical signal containing at least some of the portion of the data, and a second electrical circuitry connected with the 35 receiving arrangement and configured for receiving the second electrical signal. At least one of the transmitting and receiving arrangements includes an electron tunneling device, which includes first and second non-insulating layers spaced apart from one another such that a given voltage can 40 be provided across the first and second non-insulating layers. The electron tunneling device further includes an arrangement disposed between the first and second noninsulating layers and configured to serve as a transport of electrons between and to the first and second non-insulating 45 layers. The arrangement includes at least a first layer configured such that the transport of electrons includes, at least in part, transport by means of tunneling.

In a still further aspect of the invention, an assembly includes a first electrical circuitry for providing a first 50 electrical signal containing data, and a transmitting arrangement connected with the first electrical circuitry and configured for receiving the first electrical signal and for converting the first electrical signal into an electromagnetic magnetic signal has a carrier frequency of at least three gigahertz. The assembly further includes a receiving arrangement for receiving the electromagnetic signal and converting the electromagnetic signal into a second electrical signal containing at least some of the portion of the data, 60 and a second electrical circuitry connected with the receiving arrangement and configured for receiving the second electrical signal. At least one of the transmitting and receiving arrangements includes an electron tunneling device.

In a yet further aspect of the invention, an assembly 65 includes a first electrical circuitry for providing a first electrical signal containing data, and a transmitting arrange-

ment connected with the first electrical circuitry and configured for receiving the first electrical signal and for converting the first electrical signal into an electromagnetic signal containing at least a portion of the data. The assembly further includes a receiving arrangement for receiving the electromagnetic signal and for converting the electromagnetic signal into a second electrical signal containing at least some of the portion of the data, and a second electrical circuitry connected with the receiving arrangement and configured for receiving the second electrical signal. At least one of the transmitting and receiving arrangements includes a metal-insulator-based, electron tunneling device.

In another aspect of the invention, an assembly includes a first electrical circuitry for providing a first electrical signal containing first data, and a first transceiver arrangement connected with the first electrical circuitry and configured for receiving the first electrical signal and for converting the first electrical signal into a first electromagnetic signal containing at least a portion of the first data. The assembly further includes a second transceiver arrangement configured for receiving the first electromagnetic signal and for converting the first electromagnetic signal into a second electrical signal containing at least some of the portion of the first data, and a second electrical circuitry connected with the second transceiver arrangement and configured for receiving the second electrical signal. At least one of the first and second transceiver arrangements includes an electron tunneling device. The electron tunneling device includes first and second non-insulating layers spaced apart from one another such that a given voltage can be provided across the first and second non-insulating layers, and an arrangement disposed between the first and second non-insulating layers and configured to serve as a transport of electrons between and to the first and second non-insulating layers. The arrangement includes at least a first layer configured such that the transport of electrons includes, at least in part, transport by means of tunneling.

In still another aspect of the invention, an assembly includes a first electrical circuitry for providing a first electrical signal containing data, and a transmitting arrangement connected with the first electrical circuitry and configured for receiving at least the first electrical signal and for converting the first electrical signal into an electromagnetic signal containing at least a portion of the data. The assembly further includes a receiving arrangement for receiving the electromagnetic signal and for converting the electromagnetic signal into a second electrical signal containing at least some of the portion of the data, and a second electrical circuitry connected with the receiving arrangement and configured for receiving the second electrical, signal. At least one of the transmitting and receiving arrangements is configured to provide electron tunneling and includes an antenna connected therewith.

In a further aspect of the invention, an assembly includes signal containing at least a portion of the data. The electro- 55 a first electrical circuitry for providing a first electrical signal containing data, and a transmitting arrangement connected with the first electrical circuitry and configured for receiving the electrical signal and for converting the first electrical signal into an electromagnetic signal containing at least a portion of the data. The electromagnetic signal has a carrier frequency greater than 300 GHz. The assembly also includes a receiving arrangement configured for receiving the electromagnetic signal and converting the electromagnetic signal into a second electrical signal containing at least some of the portion of data, and a second electrical circuitry connected with the receiving arrangement and configured for receiving the second electrical signal. The transmitting

arrangement and the receiving arrangement are disposed in close proximity to one another such that the electromagnetic signal is transmitted from the transmitting arrangement to the receiving arrangement at least in part by means of coupled-mode energy transfer.

In another aspect of the invention, an assembly includes a first electrical circuitry for providing a first electrical signal containing data, and a transmitting arrangement connected with the first electrical circuitry and configured for receiving the first electrical signal and for converting the first electrical signal into an electromagnetic signal containing at least a portion of the data. The assembly further includes a receiving arrangement configured for receiving the electromagnetic signal and for converting the electromagnetic signal into a second electrical signal containing at least some of the portion of data, and a second electrical circuitry connected with the receiving arrangement and configured for receiving the second electrical signal. At least one of the transmitting and receiving arrangements includes an electron tunneling device, which in turn includes first and second non-insulating layers spaced apart from one another such that a given voltage can be applied across the first and second noninsulating layers. The electron tunneling device further includes an arrangement disposed between the first and second non-insulating layers and configured to serve as a transport of electrons between and to the first and second non-insulating layers, where the arrangement includes at least a first layer configured such that the transport of electrons includes, at least in part, transport by means of tunneling. The transmitting arrangement and the receiving arrangement are disposed in close proximity to one another such that the electromagnetic signal is transmitted from the transmitting arrangement to the receiving arrangement at least in part by means of coupled-mode energy transfer.

In still another aspect of the invention, an assembly includes a substrate and an integrated circuit package supported on the substrate. The integrated circuit package includes an integrated circuit module configured for providtransceiver arrangement connected with the integrated circuit module for receiving the output electrical signal and for converting the output electrical signal into an output electromagnetic signal containing at least a portion of the output data. The assembly further includes a waveguide having a 45 first segment and a distinct, second segment, where the first segment is also supported oil the substrate and configured for receiving at least a portion of the output electromagnetic signal and directing the portion of the output electromagnetic signal toward the distinct, second segment of the 50 waveguide.

In yet another aspect of the invention, an assembly for use in a system including an integrated circuit module configured for providing an output electrical signal containing data is disclosed. This assembly for receiving the integrated 55 circuit module and extracting the output data includes a substrate and an integrated circuit package supported on the substrate. The integrated circuit package is configured for accommodating the integrated circuit module thereon, and includes a transceiver arrangement connected with the inte- 60 grated circuit module for receiving the output electrical signal and for converting the output electrical signal into an output electromagnetic signal containing at least a portion of the output data. The assembly further includes a waveguide having a first segment and a distinct, second segment. The 65 first segment is also supported on the substrate and configured for receiving at least a portion of the output electro10

magnetic signal and directing the portion of the output electromagnetic signal toward the distinct, second segment of the waveguide.

In still yet another aspect of the invention, an assembly for 5 use in a system including an integrated circuit module configured for providing an output electrical signal containing output data is disclosed. This assembly for receiving the integrated circuit module and extracting the output data includes an integrated circuit package configured for accommodating the integrated circuit module thereon. The integrated circuit package includes a transceiver arrangement connected with the integrated circuit module and configured for receiving the output electrical signal, converting the output electrical signal into an output electromagnetic signal containing at least a portion of the output data, and directing the output electromagnetic signal away from the integrated circuit package.

In another aspect of the invention, an assembly includes a substrate and an integrated circuit package. The integrated circuit package includes an integrated circuit module for providing an output electrical signal containing output data, and a plurality of electrical pin-outs for directing the output electrical signal away from the integrated circuit module and away from the integrated circuit package. The assembly further includes a socket arrangement supported on the substrate and configured for receiving the integrated circuit package thereon. The socket arrangement includes a transceiver arrangement disposed therein such that the transceiver arrangement receives the output electrical signal from the plurality of electrical pin-outs and converts the output electrical signal into an output electromagnetic signal containing at least a portion of the output data. The assembly also includes a waveguide having a first segment and a distinct, second segment, where the first segment is also 35 supported on the substrate and is configured for receiving at least a portion of the output electromagnetic signal and directing the portion of the output electromagnetic signal toward the distinct, second segment of the waveguide.

In still another aspect of the invention, an assembly for ing an output electrical signal containing output data, and a 40 use in a system including an integrated circuit package is disclosed. The integrated circuit package includes an integrated circuit module, for providing an output electrical signal containing output data, and a plurality of electrical pin-outs, for directing the output electrical signal away from the integrated circuit module and away from the integrated circuit package is disclosed. This assembly for receiving the integrated circuit module and extracting the output data, includes a substrate and a socket arrangement supported on the substrate and configured for receiving the integrated circuit package thereon. The socket arrangement includes a transceiver arrangement disposed therein such that the transceiver arrangement receives the output electrical signal from the plurality of electrical pin-outs and converts the output electrical signal into an output electromagnetic signal containing at least a portion of the output data. The assembly further includes a waveguide having a first segment and a distinct, second segment. The first segment is also supported on the substrate and is configured for receiving at least a portion of the output electromagnetic signal and directing the portion of the output electromagnetic signal toward the distinct, second segment of the waveguide.

> In yet another aspect of the invention, an assembly for use in a system including an integrated circuit package is disclosed. The integrated circuit package includes an integrated circuit module, for providing an output electrical signal containing output data, and a plurality of electrical pin-outs, for directing the output electrical signal away from

11

the integrated circuit module and away from the integrated circuit package. This assembly for receiving the integrated circuit module and extracting said output data includes a socket arrangement configured for accommodating the integrated circuit package thereon. The socket arrangement 5 includes a transceiver arrangement configured for receiving the output electrical signal from the plurality of electrical pin-outs, converting the output electrical signal into an output electromagnetic signal containing at least a portion of the output data, and directing the output electromagnetic 10 signal away from the socket arrangement.

In another aspect of the invention, an assembly includes a substrate and an integrated circuit package supported on the substrate and containing an integrated circuit module. The integrated circuit module is configured for providing an 15 output electrical signal containing output data. The assembly also includes an electrical interconnect also supported on the substrate and having first and second ends, where the first end is connected with the integrated circuit module through the integrated circuit package and is configured to receive 20 the output electrical signal such that the output electrical signal is directed through the electrical interconnect toward the second end. The assembly further includes a transceiver package also supported on the substrate and including a transceiver chip. The transceiver chip is connected with the 25 second end of the electrical interconnect such that the transceiver chip receives the output electrical signal and converts the output electrical signal into an output electromagnetic signal containing at least a portion of the output data. Additionally, the assembly includes a waveguide hav- 30 ing a first segment and a distinct, second segment. The first segment is also supported on the substrate and configured for receiving at least a portion of the output electromagnetic signal and directing the portion of the output electromagnetic signal toward the distinct, second segment of the 35

In yet another aspect of the invention, an assembly for use in a system including an integrated circuit package is disclosed. The integrated circuit package includes an integrated circuit module configured for providing an output 40 electrical signal containing output data. This assembly for receiving the integrated circuit module and extracting the output data includes a substrate configured for supporting the integrated circuit module thereon. The substrate includes an electrical interconnect having first and second ends. The 45 first end is connected with the integrated circuit module through the integrated circuit package and is configured to receive the output electrical signal such that the output electrical signal is directed through the electrical interconnect toward the second end. The substrate also includes a 50 transceiver package including a transceiver chip. The transceiver chip is connected with the second end of the electrical interconnect such that the transceiver chip receives the output electrical signal and converts the output electrical signal into an output electromagnetic signal containing at 55 least a portion of the output data. The substrate further includes a waveguide having a first segment and a distinct, second segment. The first segment is configured for receiving at least a portion of the output electromagnetic signal and directing the portion of the output electromagnetic signal 60 toward the distinct, second segment of the waveguide.

In still another aspect of the invention, an assembly for use in a system including an integrated circuit package is disclosed. The integrated circuit package includes an integrated circuit module configured for providing an output 65 electrical signal containing output data. This assembly for receiving the integrated circuit module and extracting the

12

output data includes an electrical interconnect having first and second ends. The first end is connected with the integrated circuit module through the integrated circuit package and is configured to receive the output electrical signal such that the output electrical signal is directed through the electrical interconnect toward the second end. The assembly also includes a transceiver package including a transceiver chip. The transceiver chip is connected with the second end of the electrical interconnect and is configured for receiving the output electrical signal, converting the output electrical signal into an output electromagnetic signal containing at least a portion of the output data, and directing the output electromagnetic signal away from the transceiver package.

# BRIEF DESCRIPTION OF THE SEVERAL VIEWS OF THE DRAWING

The present invention may be understood by reference to the following detailed description taken in conjunction with the drawings briefly described below. It is noted that, for purposes of illustrative clarity, certail elements in the drawings may not be drawn to scale.

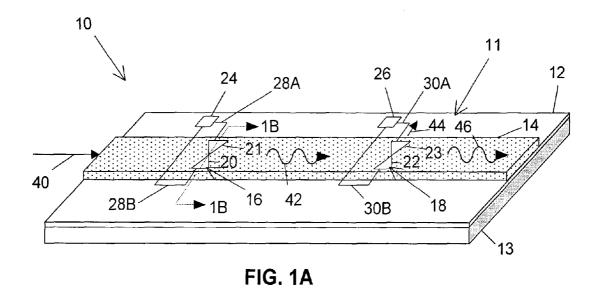

FIG. 1A is a diagrammatic illustration, in perspective view, of an interconnected electron tunneling device of the present invention, shown here to illustrate an embodiment including a planar waveguide on a chip as the interconnection

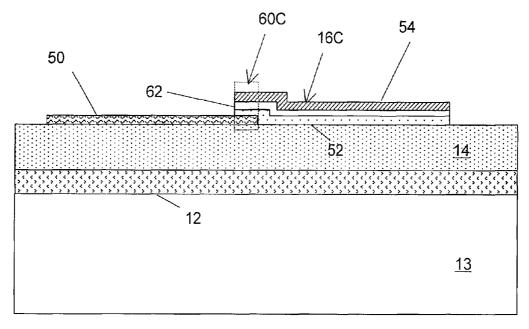

FIGS. 1B and 1C are diagrammatic illustrations, in crosssection, showing details of electron tunneling devices suitable for use in the interconnected electron tunneling device of the present invention.

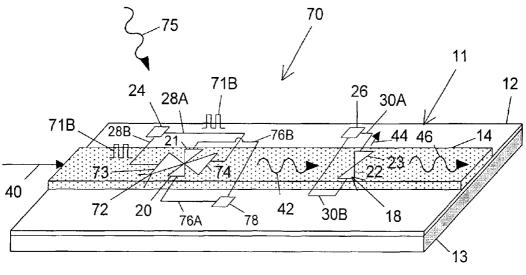

FIG. 1D is a diagrammatic illustration, in perspective view, of an alternative embodiment of an interconnected electron tunneling device of the present invention, shown here to illustrate the use of a double antenna electron tunneling device.

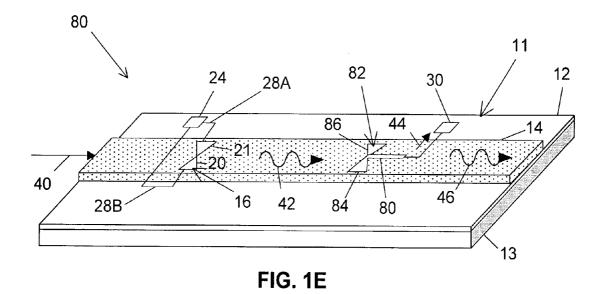

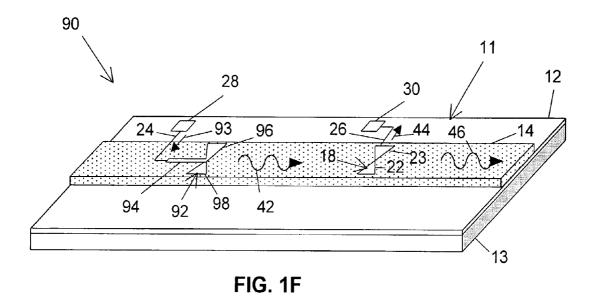

FIGS. 1E and 1F are diagrammatic illustrations, in perspective view, of additional embodiments of an interconnected electron tunneling device of the present invention, shown here to illustrate the use of surface plasmon devices.

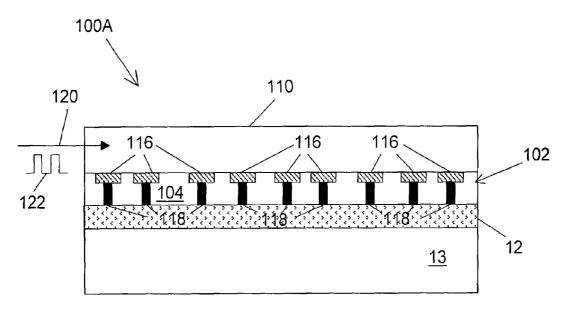

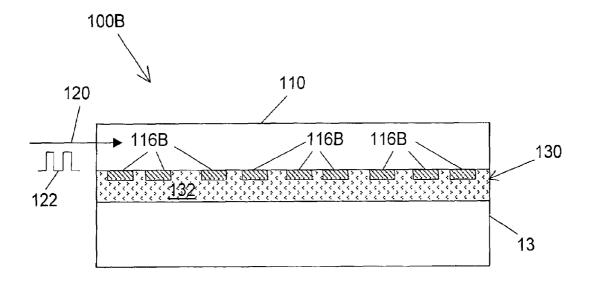

FIGS. 2A and 2B are diagrammatic illustrations, in crosssection, of embodiments of an edge-fed, optical clock distribution scheme of the present invention.

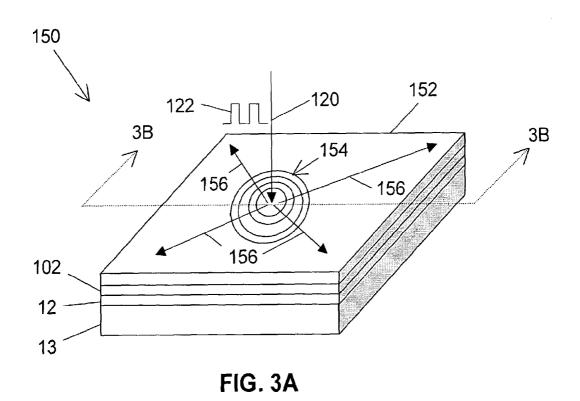

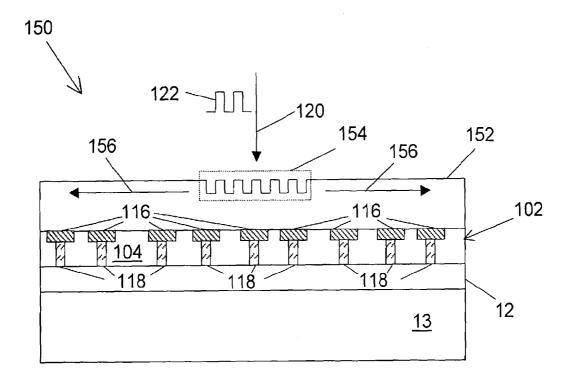

FIGS. 3A and 3B are diagrammatic illustrations of a top-fed, optical clock distribution scheme of the present invention.

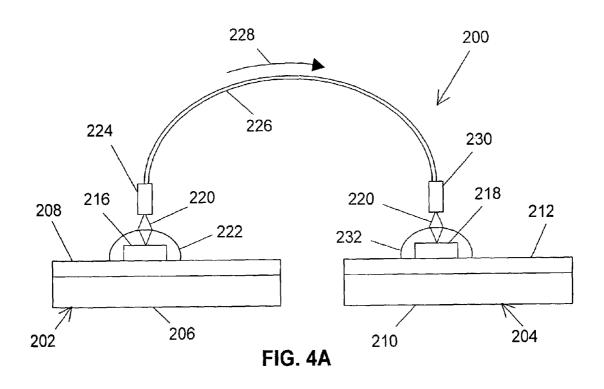

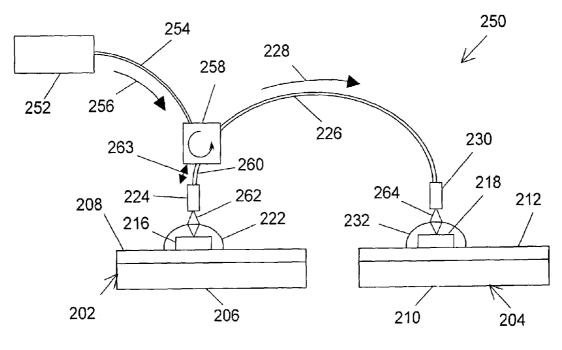

FIGS. 4A–4D are diagrammatic illustrations of another interconnected electron tunneling device of the present invention, shown here to illustrate embodiments including optical fiber as the interconnection between devices on separate chips.

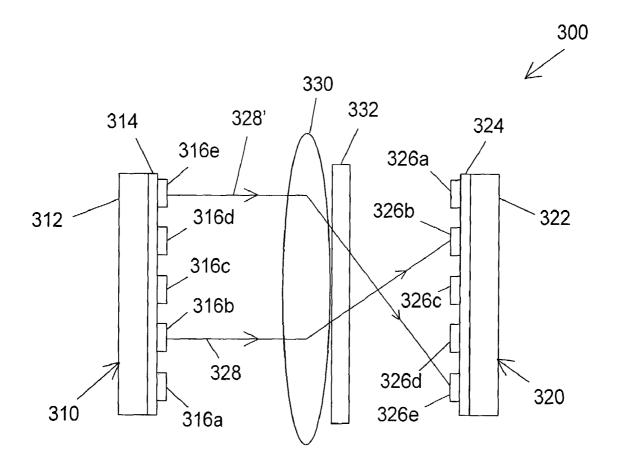

FIG. 5 is a diagrammatic illustration of still another interconnected electron tunneling device in accordance with the present invention, shown here to illustrate the use of free-space optical interconnection between electron tunneling devices on separate chips.

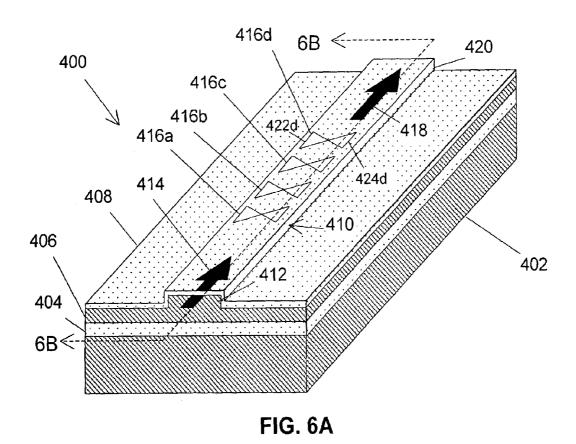

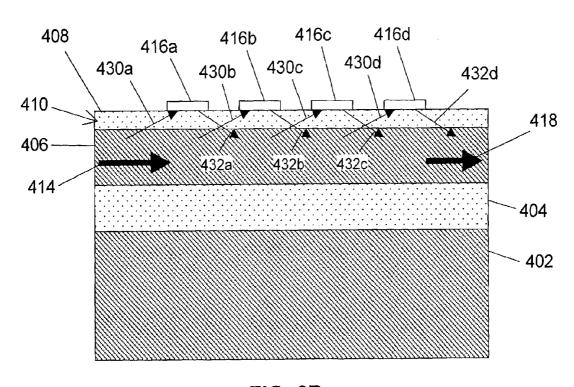

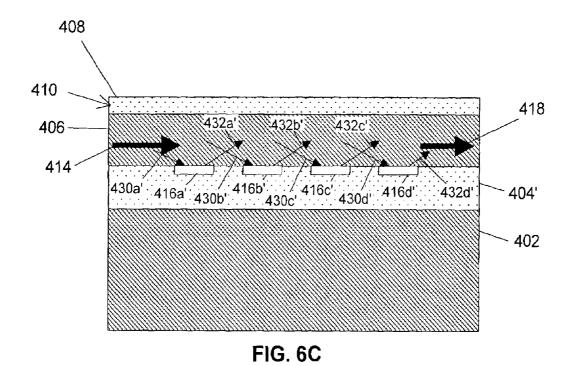

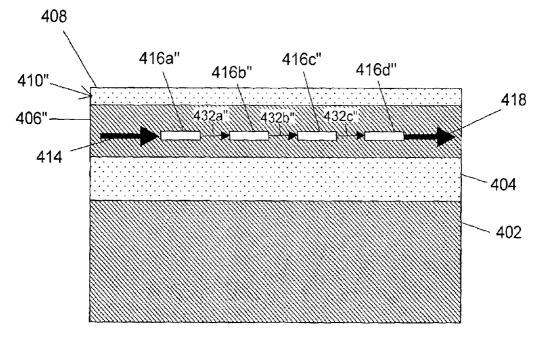

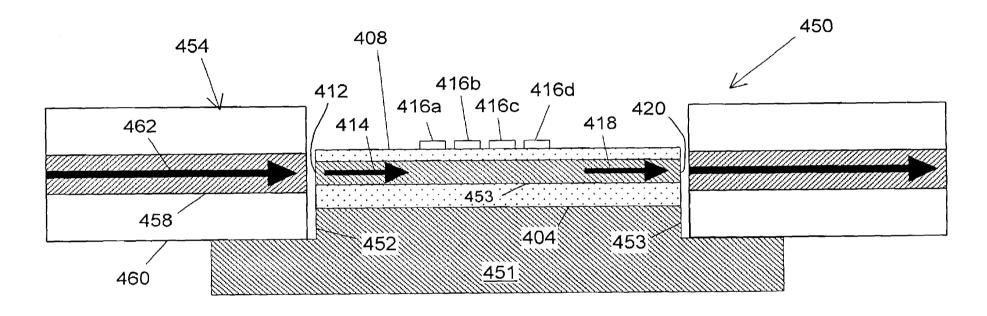

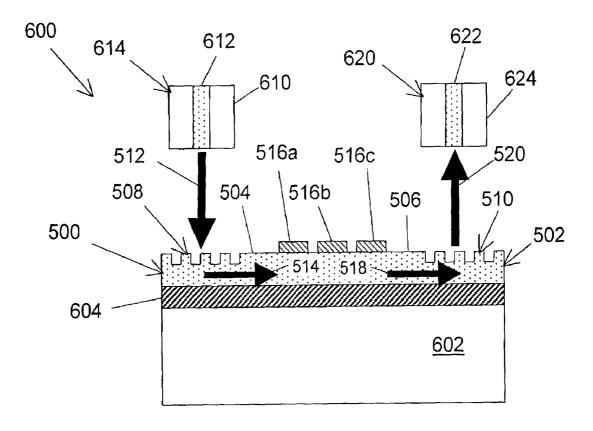

FIGS. 6A–6E are diagrammatic illustrations of a waveguide-coupled device of the present invention, shown here to illustrate various embodiments of the coupling of electron tunneling devices with a waveguide, as used in the aforementioned interconnected electron tunneling devices.

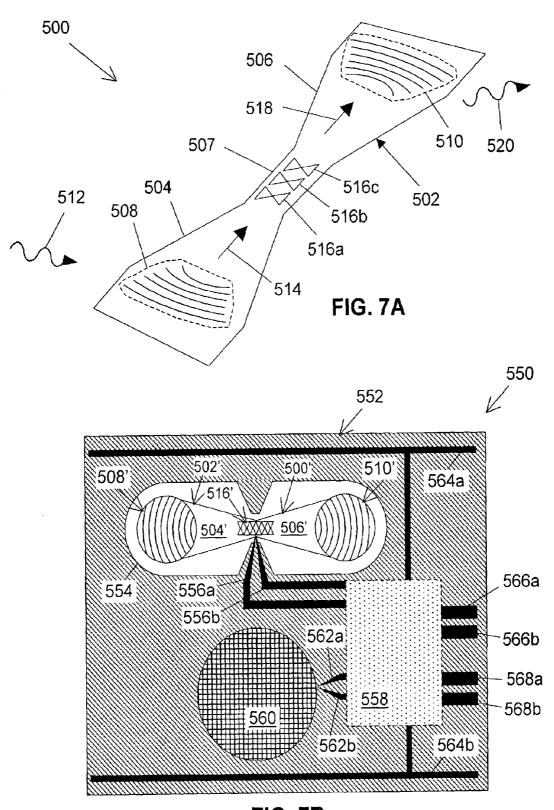

FIGS. 7A–7D are diagrammatic illustrations of an alternative waveguide-coupled device of the present invention and applications.

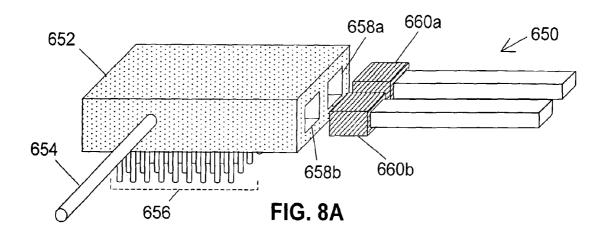

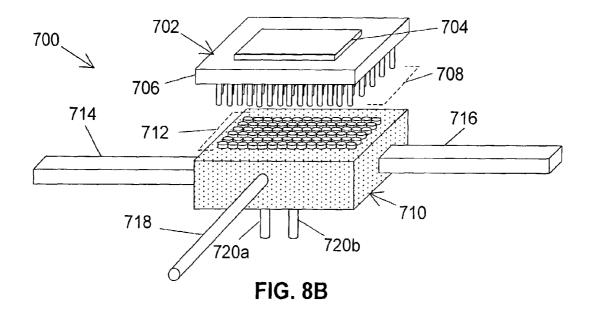

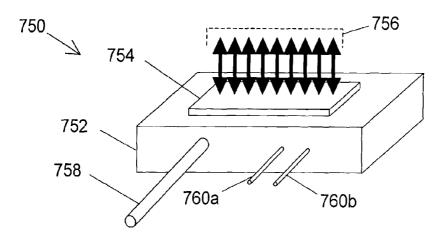

FIGS. 8A-8C are diagrammatic illustrations, in perspective view, of examples of packaging options and applications for the waveguide-coupled device of the present invention.

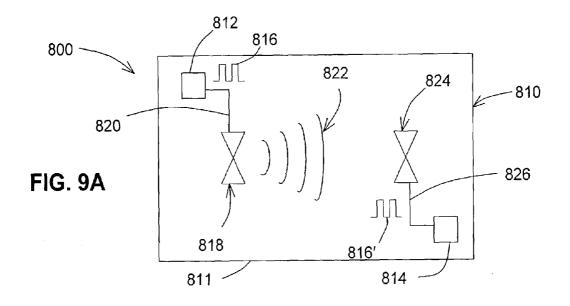

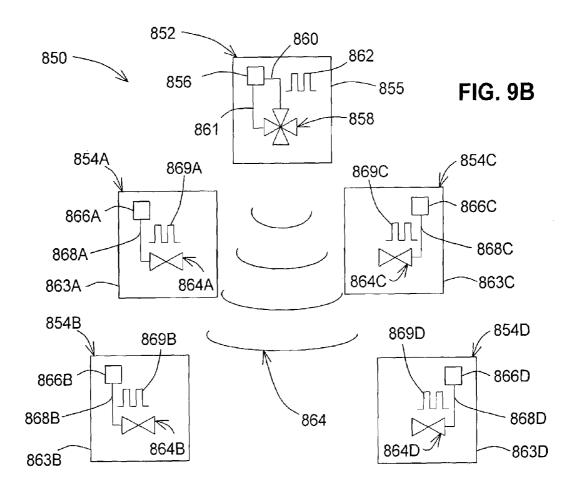

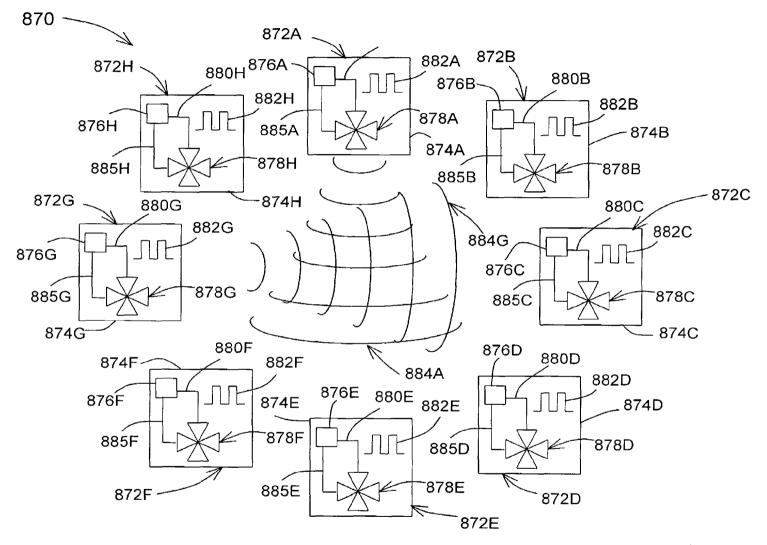

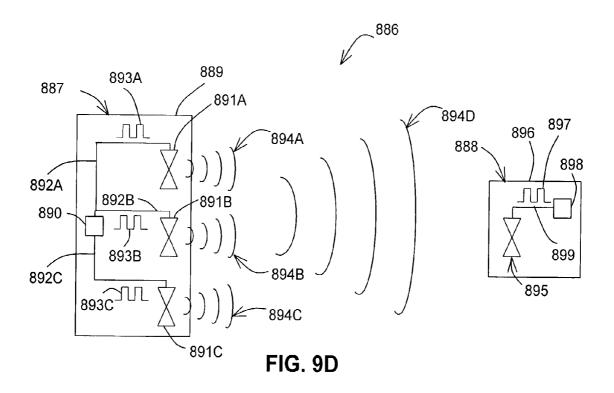

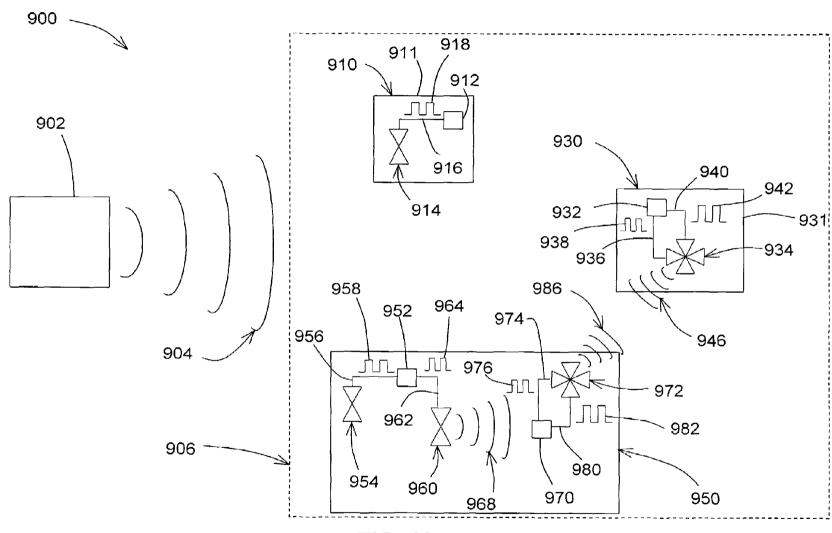

FIGS. 9A-9D are diagrammatic illustrations of examples of layout configurations for a terahertz interconnect system in accordance with the present invention.

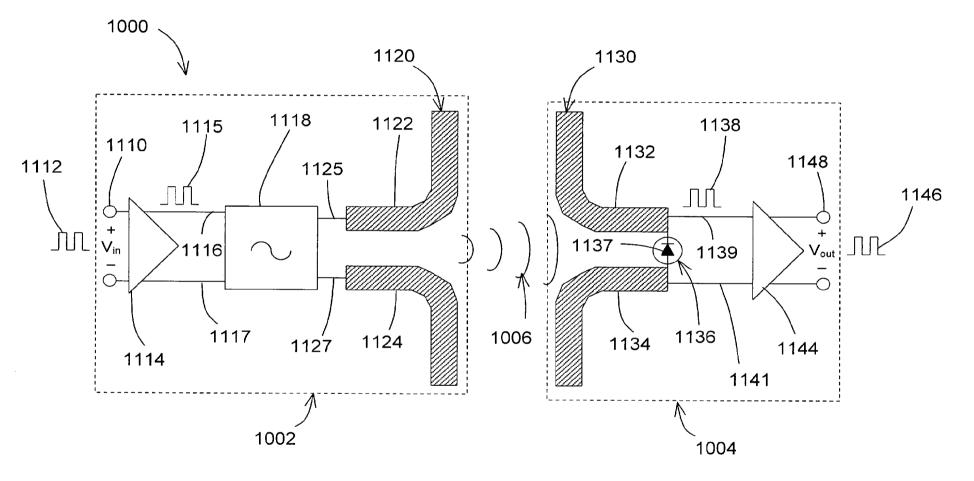

FIG. 10 is a diagrammatic illustration of a power/clock distribution scheme designed in accordance with the present 5 invention.

FIG. 11 is a diagrammatic illustration of a terahertz optocoupler designed in accordance with the present invention

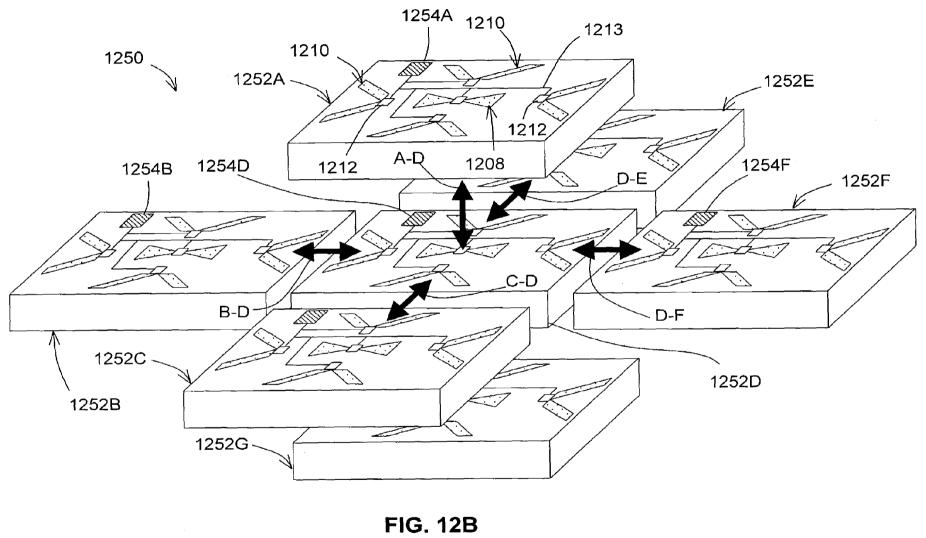

FIGS. 12A and 12B are diagrammatic illustrations, in 10 perspective view, of examples of a three-dimensional interconnection system designed in accordance with the present invention

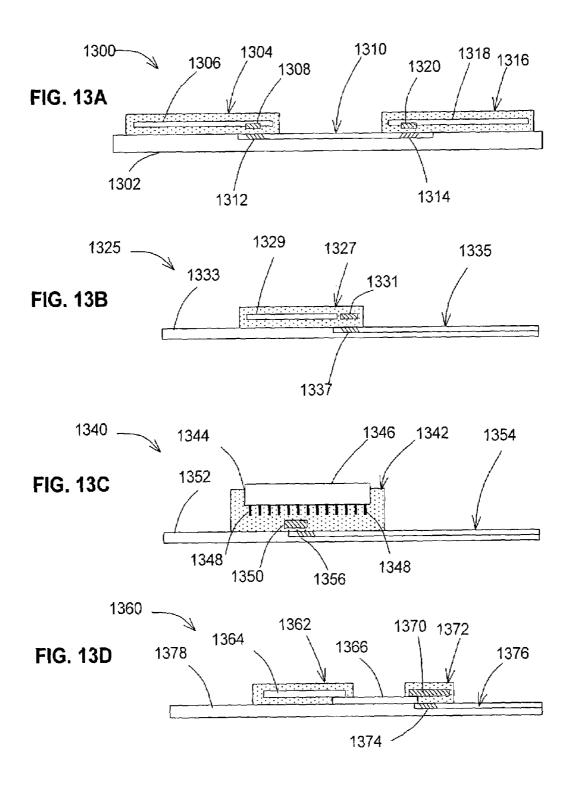

FIGS. 13A–13D are diagrammatic illustrations of assemblies for integrating electrical circuitry such as, for example, 15 standard integrated circuit chips, into the terahertz interconnect system of the present invention.

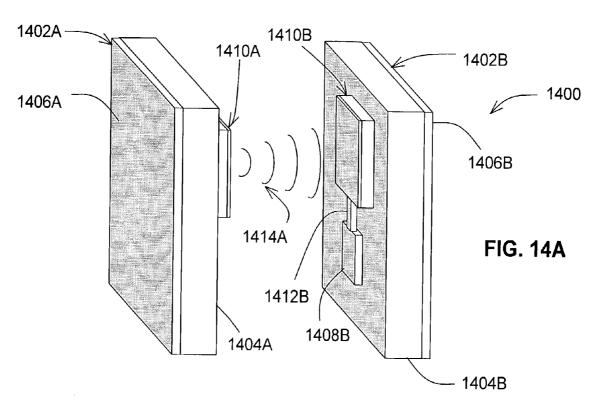

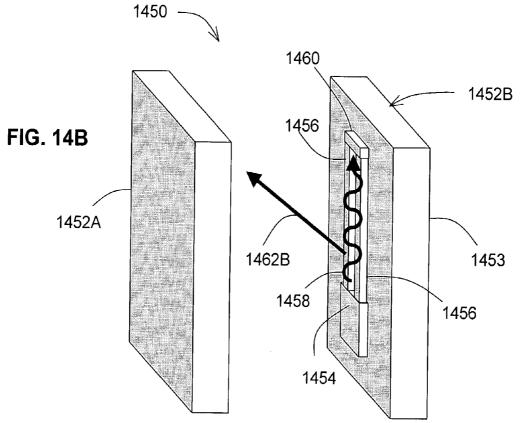

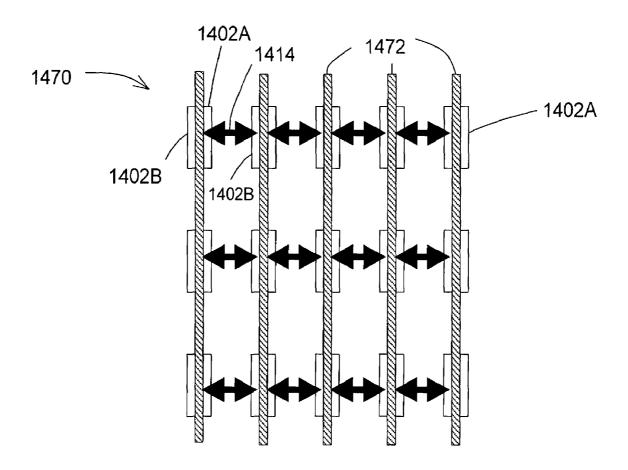

FIGS. 14A-14C are diagrammatic illustrations of a board-to-board interconnection scheme based on the terahertz interconnect of the present invention. FIG. 14A a 20 diagrammatic illustration of a side view of a plurality of boards interconnected by a plurality of interconnected, transceiver chip pairs, while FIGS. 14B-14C are diagrammatic illustrations, in perspective view, of two examples of pairs of interconnected, transceiver chips in accordance with 25 the present invention.

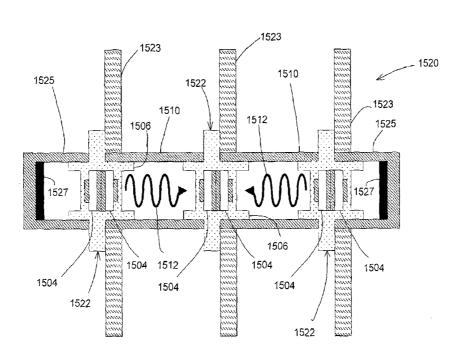

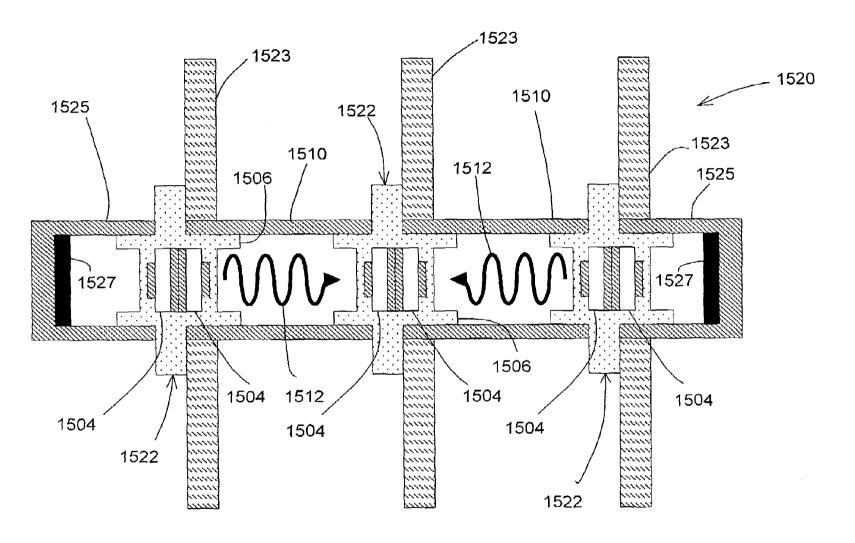

FIGS. 15A–15C are diagrammatic illustrations of terahertz interconnect systems including guided wave configurations in accordance with the present invention.

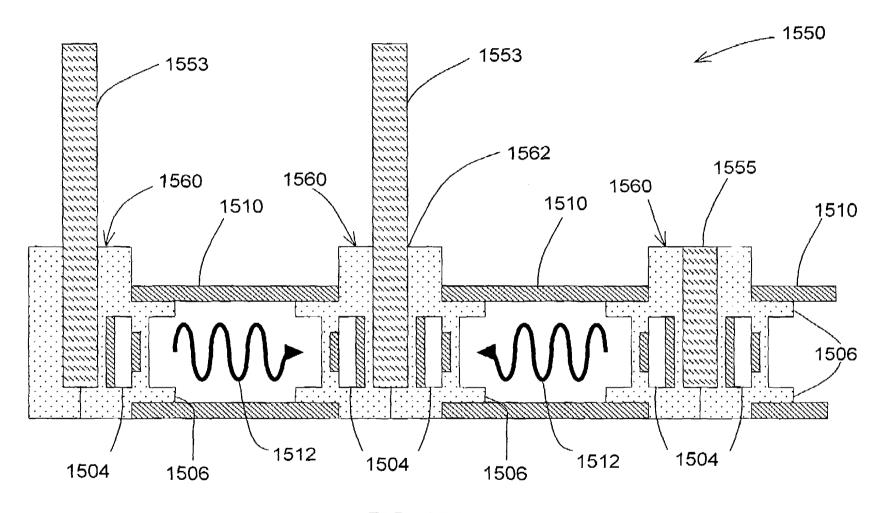

FIGS. 16A-16C are diagrammatic illustrations of 30 embodiments of the terahertz interconnect system of the present invention, shown here to illustrate an example of a transmitter/receiver pair including coupled transmission lines on a surface of a substrate (FIG. 16A), a close-up of the coupled transmission lines (FIG. 16B), and an alternative 35 arrangement of the transmitter and receiver on opposing faces of a substrate (FIG. 16C).

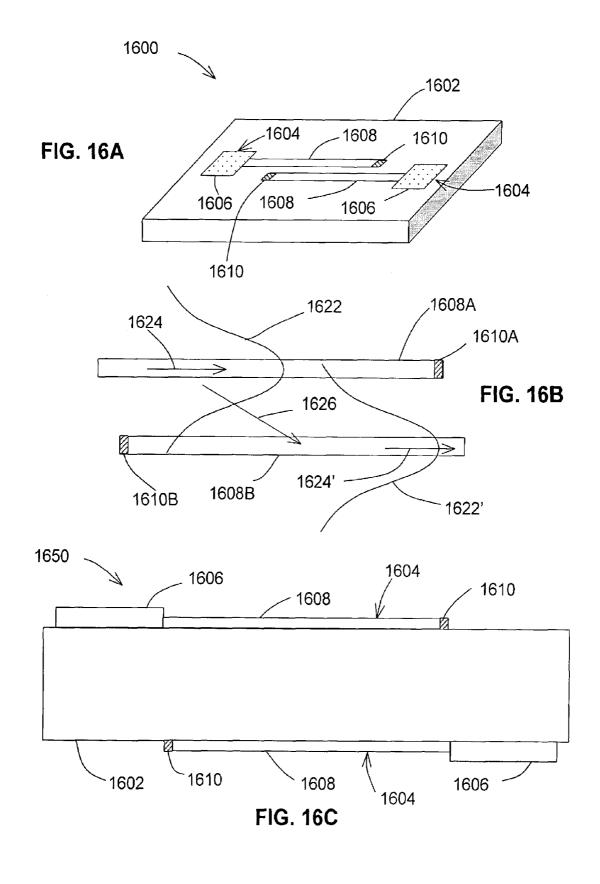

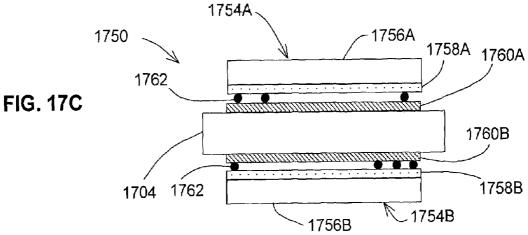

FIGS. 17A–17C are diagrammatic illustrations, in crosssection, of exemplary embodiments of coupling schemes to establish communication between two electronic circuitry 40 on two separate substrates, such as two integrated circuit chips, based on the terahertz interconnect system of the present invention.

## DETAILED DESCRIPTION

The following description is presented to enable one of ordinary skill in the art to make and use the invention and is provided in the context of a patent application and its requirements. Various modifications to the described 50 embodiments will be readily apparent to those skilled in the art and the generic principles herein may be applied to other embodiments. Thus, the present invention is not intended to be limited to the embodiment shown but is to be accorded the widest scope consistent with the principles and features 55 described herein.

As described in the Background section, there is a growing need for high speed interconnection between devices over short distances, such as between racks, boards, chips, as well as between components located on a single chip. These 60 interconnection arrangements must be capable of high speed transmission of data and should be low cost. The interconnection arrangements and systems need to be competitive and compatible with current state-of-the-art electrical interconnects in terms of cost, speed, power, distance, requirement for signal processing and allowance of plug-n-play. For low cost, high speed and highest level of integration, the

14

interconnect components may be integrated directly onto silicon integrated circuitry. The interconnect should ideally be compatible with standardized systems and interfaces provided by existing suppliers. In order to accommodate the current state of the technology, the interconnect should be compatible with multi-mode fibers and be time division multiplexing (TDM) or coarse wavelength division multiplexing (CWDM) compatible. Alternatively, depending on the application in which the interconnect is to be used, single-mode fibers might also be used. Polarization-insensitivity is desirable in order to reduce signal loss. VCSEL devices are the mainstay light sources in the current art; therefore the interconnection arrangement should be compatible with VCSEL devices. Currently-available VCSEL devices operate at 850 nm and, potentially, at 1300 and 1550 nm wavelengths. Furthermore, current VCSELs operate at 2.5 Gbps, while 10 Gbps and, in the future, 80 Gbps devices may be available. The interconnect should also be temperature-insensitive in order for the interconnect to be incorporated onto silicon integrated circuitry. For example, as will be described in detail hereinafter, the interconnect may be top-side coupled onto CMOS-integrated components.

Recent progress in tunneling junction technology by the assignee of the present application has greatly increased the flexibility in fabrication and design of electron tunneling devices based on metal-insulator(s)-metal structures, thus allowing the fabrication of high speed electron tunneling devices. For example, see aforementioned U.S. Pat. No. 6,534,784 (hereinafter, P1 patent), U.S. Pat. No. 6,563,185 (hereinafter, P2 patent) and U.S. patent application Ser. No. 10/103,054 (hereinafter, P3 application), Ser. No. 10,140, 545 (hereinafter P3-cip application), Ser. No. 10/265,935 (hereinafter P1-cip application) and Ser. No. 10/337,427 (hereinafter P5 application). All of the aforementioned patents and applications are incorporated herein by reference in their entirety.

As described in the P5 application, the electron tunneling devices as disclosed in the aforementioned P1 and P2 patents as well as P3, P3-cip and P1-cip applications are particularly suited for integration onto existing chips because combination of metal and insulating layers forming each electron tunneling device may be deposited directly on the chips without the need for additional semiconductor processing steps. That is, the electron tunneling devices of 45 the aforementioned applications may be formed monolithically on existing semiconductor devices without high temperature or crystalline growth procedures. Additionally, unlike hybrid integration assemblies, in which separatelyfabricated devices are surface mounted or flip-chip bonded onto existing chips, the electron tunneling devices developed by the assignee of the present invention may be formed directly on the chips themselves. Furthermore, as described in detail in the P1 and P2 patents and P3, P3-cip and P1-cip applications, the electron tunneling devices as disclosed in these applications are capable of operating at high speeds, thus enabling these devices to function in optical regimes and at high data rates. Still further, the electron tunneling devices may be integrated into the circuitry itself (i.e., formned during the fabrication procedure of the circuitry as a part of the circuitry components), if so desired. Therefore, by incorporating the electron tunneling devices of the aforementioned P1 and P2 patents and P3, P3-cip and P1-cip applications as part of an optical interconnect assembly, a high speed interconnection solution for use between components on chips, between chips and so on may be attained.

Moreover, the electron tunneling devices developed by the assignee of the present invention may be fabricated

directly adjacent to a waveguide and be configured to cooperate with the waveguide so as to absorb an evanescent field portion of a lightwave traveling through the waveguide. For example, the electron tunneling device may include an antenna designed to couple light of a particular wavelength 5 (e.g., optical wavelengths) out of the waveguide and into a tunneling junction region of the electron tunneling device. Alternatively, the electron tunneling devices may be fabricated within a waveguide so as to absorb the propagating field portion of the a lightwave traveling through the 10 waveguide. As will be discussed in detail at an appropriate point in the text below, the concept of combining the electron tunneling devices with a waveguide is significant in that it allows the coupling of light energy into and out of the waveguide as well as the directing of light energy to 15 electronic devices as electrical energy. This concept may be utilized to provide high speed interconnections between optical and electronic components, as will be discussed in detail immediately hereinafter.

Turning now to the drawings, wherein like components 20 are indicated by like reference numbers throughout the various figures, attention is immediately directed to FIG. 1A, which illustrates an approach to the interconnection of two electron tunneling structures on a chip in accordance with the present invention. FIG. 1A is a diagrammatic 25 illustration, in perspective view, of an interconnect assembly 10. Interconnect assembly 10 includes a chip 11, which includes circuitry 12 formed on top of a substrate 13. A waveguide region 14 is defined on chip 11, and a first electron tunneling device 16 and a second electron tunneling 30 device 18 are formed on top of waveguide region 14. First and second electron tunneling devices 16 and 18 may be, for instance, high speed electron tunneling devices and variants as disclosed in the aforementioned P1 and P2 patents and P3, P3-cip and P1-cip applications, which high speed electron 35 tunneling devices are formed of thin film layers of noninsulating and insulating materials. Waveguide region 14 may be formed, for example, of polymers, dielectric materials such as glass, fused silica and silicon-on-insulator, photonic bandgap materials. In the embodiment illustrated in FIG. 1A, first and second electron tunneling devices 16 and 18 include antenna arms 20A-20B and 22A-22B, respectively, defining bowtie antennae. Other antenna designs such as, but not limited to, Vivaldi, Vee, and those 45 designs described in the P1-cip application, may also be used. First and second electron tunneling devices 16 and 18 may be connected to integrated electronic components in the existing electronic circuitry (represented by squares 24 and 26) on the chip by, for example, pairs of metal lines 28A and 50 28B and 30A and 30B, respectively. The integrated electronic components 24 and 26 may be, for example, driver transistors or amplifier transistors.

Still referring to FIG. 1A, a number of different configurations of the interconnect assembly of the present invention 55 are contemplated. As an example, first electron tunneling device 16 may be a modulator, as described in the P2 patent or P3 or P3-cip application, and second electron tunneling device 18 may be a detector, as described in the aforementioned P1 and P2 patents and P3, P3-cip and P1-cip appli- 60 cations. In this case, an external continuous wave (CW) light source (not shown) may feed a CW light, indicated by an arrow 40, into waveguide 14, then the circuitry on the chip may cause first electron tunneling device 16 (modulator) to modulate the CW light in the waveguide so as to produce a 65 modulated light, indicated by a wavy arrow 42. The manner in which the first electron tunneling device may act as a

16

modulator is described in detail in the aforementioned P2 patent and P3 applications. Waveguide region 14 may be further configured to act as an interconnect between the first electron tunneling device 16 and second electron tunneling device 18 such that second electron tunneling device 18 (detector) detects modulated light 42 to generate an electrical signal, indicated by an arrow 44. Electrical signal 44 can then be directed back into the existing circuitry on the chip or be coupled out to integrated electronic component 26. Alternatively, second electron tunneling device 18 may be configured to detect only a portion of modulated light 42 such that a slightly attenuated, output light, indicated by a wavy arrow 46, is further directed through waveguide 14 to be coupled out of the chip. As yet another alternative, second electron tunneling device 18 may be replaced by a conventional detector which is not based on electron tunneling such as, for example, a semiconductor-based detector.

Continuing to refer to FIG. 1A, interconnect assembly 10 is advantageous in that an optical means of interconnecting various devices on-chip as well as off-chip is provided without additional complications in the chip circuitry itself. As described in detail in the aforementioned P1 and P2 patents and P3 application, the electron tunneling devices disclosed by the assignee of the present invention may be formed of readily depositable materials, such as metals and insulators. As a result, first electron tunneling device 16 may be formed directly on top of a chip, as shown in FIG. 1A, without interference with the intended function of the integrated electronic components in the chip circuitry or displacing existing circuitry on the chip, using relatively simple, deposition and lithography, rather than semiconductor crystalline growth techniques. Also, rather than relying upon a direct, hardwire electrical connection from the portion of the chip circuitry near component 24 to that near component 26, data may be transferred between the two regions on the chip by the optical interconnection between the first electron tunneling device and the second electron tunneling device. Furthermore, modulated light 46, which contains information as encoded onto first electron tunneling photonic crystals, lithium niobate, organic materials and 40 device 16 acting as a modulator, may be directed onto a site away from chip 11 such that the encoded information is transmitted off-chip at optical speeds.

Referring now to FIGS. 1B and 1C, possible configurations for the electron tunneling devices shown in FIG. 1A are described. FIG. 1B illustrates a cross-sectional view of one embodiment of an electron tunneling device suitable for use in the interconnect assembly of the present invention as shown in FIG. 1A. This electron tunneling device is similar in design to those shown in the aforementioned P1 and P2 patents. An electron tunneling device 16B includes a first non-insulating layer 50, which forms one of the antenna arms (e.g., antenna arm 20 in FIG. 1A) of the first electron tunneling device. In the embodiment shown in FIG. 1B, first non-insulating layer 50 is deposited on top of waveguide 14, which in turn has been formed on top of circuitry 12. First non-insulating layer 50 may be, for example, a metal, semi-metal, semiconductor or superconductor. A first layer 52 is deposited also on top of waveguide 14 such that first layer 52 partially overlaps first non-insulating layer 50. First layer 52 may be, for example, an amorphous or crystalline insulating material. The portion which overlaps with first non-insulating layer 50 may be, for instance, an oxide of the first non-insulating layer or a separately deposited, amorphous insulating layer. A second non-insulating layer 54 is deposited on top of first layer 52 such that a tunneling junction region 60B is formned by the overlapping portions of first non-insulating layer 50, first layer 52 and second

non-insulating layer 54. Second insulating layer 54 defines the other of the antenna arms (e.g., antenna arm 21 in FIG. 1A) of first electron tunneling device 16B, and may be formned of, for example, a metal, semi-metal, semiconductor or superconductor. In a tunneling junction region (indicated by a dashed box 60B), first and second non-insulating layers are spaced apart from one another such that a voltage (not shown) may be applied thereacross. First layer 52 is further configured to cooperate with the materials forming the first and second non-insulating layers such that electrons 10 are allowed to travel therethrough by means of tunneling depending on the voltage placed across the first and second non-insulating layers. That is, the thickness of first layer 52 as well as the material from which the first layer is formned are selected such that first electron tunneling device exhibits 15 the desired electron tunneling characteristics. For instance, the first non-insulating layer may be 40 nm of nickel, and the second non-insulating material may also be 40 nm of nickel, both deposited by sputtering. The first layer may consist of, for example, a layer of nickel oxide, 4 nm thick, formed by 20 thermal oxidation.

17

Referring now to FIG. 1C, a variation of the electron tunneling device of FIG. 1B is illustrated. An electron tunneling device 16C is based on the structures described in the co-assigned P1 patent mentioned earlier. Like electron 25 tunneling device 16B shown in FIG. 1B, electron tunneling device 16C includes first and second non-insulating layers 50 and 54, respectively, with a first layer 52 disposed therebetween. Additionally, a tunneling region 60C of electron tunneling device 16C includes a second layer 62. As 30 described in detail in the P1 patent, the addition of second layer 62 serves to increase the nonlinearity in the currentvoltage characteristics of the electron tunneling device. Moreover, the inclusion of the second layer allows the possibility of resonant tunneling as the electron transport 35 mechanism through the electron tunneling device. Second layer 62 may be, for example, an amorphous or crystalline insulating layer. For instance, the first non-insulating layer may be 40 mn of niobium, and the second non-insulating material may be 40 nm of tantalum, both deposited by 40 sputtering. The first layer may consist of amorphous niobium oxide, 1.5 nm thick, on top of which is deposited amorphous tantalum oxide, also 1.5 nm thick, both deposited by atomic layer deposition.

It should be noted that, the modifications shown in FIGS. 45 1B and 1C may be applied to one or both of first and second electron tunneling devices 16 and 18 of FIG. 1A. Additional modifications, such as the addition of three or more adjacent insulating layers or a combination of metal and insulating layers between the first and second non-insulating layers as 50 shown in FIGS. 1B and 1C, are also contemplated and discussed in the aforementioned co-assigned U.S. patent applications.

Additional variations on the interconnect assembly of the present invention are shown in FIGS. 1D–1F. FIG. 1D is 55 similar to the interconnect assembly shown in FIG. 1A, but first electron tunneling device 16 has been replaced with an electron tunneling modulator 72. Electron tunneling modulator 72 includes first and second pairs of antenna arms. First pair of antenna arms 20 and 21 is essentially the same as that 60 shown in, for example, FIG. 1A, and is designed to receive input light 40 and modulate it so as to produce modulated light 42. As discussed in reference to FIGS. 1B and 1C, antenna arms 20 and 21 may be configured to overlap such that a tunneling junction region (not shown) is formed. 65 Electrical signals 71A and/or 71B may be provided via wires 28A and 28B, respectively, as a modulation signal so as to

18

vary the electron transport characteristics of the tunneling junction region, thus yielding the modulated light in accordance with the modulation signal. Electron tunneling device 72 further includes a second pair of antenna arms 73 and 74, which may be configured to receive an optical modulation input 75. Optical modulation input 75 acts as an optical modulation signal to vary the electron transport characteristics of the tunneling junction region, thus, again, such that electron tunneling device 72 yields modulated light 42 in accordance with the optical modulation signal. Details of such a crossed-bowtie antenna modulator are disclosed in the aforementioned P2 patent. Additionally, second pair of antenna arms 73 and 74 may be connected with an integrated electronic component 78 in circuitry 12 via wires 76A and 76B.

FIG. 1E shows yet another alternative embodiment of an interconnect assembly 80, this time using a surface plasmon device of the P3 application as a detector device, in place of second electron tunneling device 18 in interconnect assembly 10 of FIG. 1A. A surface plasmon device 82 includes a pair of antenna arms 84 and 86, which are configured to receive modulated light 42 from first electron tunneling device 16. Antenna arms 84 and 86 direct the modulated light so received into a surface plasmon waveguide region 88 as surface plasmon waves. Surface plasmon waveguide region 88 then provides electrical signal 44 in accordance with the received modulated light.

As yet another alternative, an interconnect assembly 90, as shown in FIG. 1F, may include a surface plasmon device 92 acting as an emitter, such as described in the P3 application. For instance, in interconnect assembly 90 as shown in FIG. 1F, surface plasmon device 92 receives an electrical signal 93 from integrated electrical component 28, which is a part of the chip circuitry. The received electrical signal generates surface plasmon waves (not shown) in a surface plasmon waveguide region 94. A pair of antenna arms 96 and 98 of surface plasmon device 92 acts as an emitter antenna to emit the generated surface plasmon waves as an output light 46.

FIGS. 1A–1F illustrate interconnect assemblies in which light coupling from the waveguide into and out of electron tunneling devices and surface plasmon devices is performed using antennae. It should be noted that other light coupling schemes are also possible. For example, as disclosed in the P3 application, surface plasmon evanescent couplers and grating couplers may also be used in the interconnect assembly of the present invention.

An application of the interconnect assembly of the present invention is shown in FIGS. 2A and 2B. FIG. 2A illustrates a cross-sectional view of an integrated circuit chip 100A including an optical clock distribution configuration. Integrated circuit chip 100A includes circuitry 12 disposed on substrate 13 as discussed earlier. Integrated circuit chip 100A also includes a tunneling device layer 102 based on an insulator 104 with a waveguide layer 110 disposed thereon. Tunneling device layer 102 includes two or more electron tunneling devices 116, which are connected to circuitry 12 through, for example, vias 118. Each one of the electron tunneling devices may be configured as a detector as described, for example, in the P1 and P2 patents and P3 application. In the integrated circuit chip shown in FIG. 2A, an optical signal 120, carrying a clock signal shown as a waveform 122, is edge-coupled into waveguide layer 110. Optical signal 120 may have a sufficiently long wavelength (e.g., 1550 nm) such that the optical signal is not absorbed by, for example, a silicon substrate or silicon components in the circuitry but only by the electron tunneling devices. As

optical signal 120 is guided through waveguide layer 110, each one of electron tunneling devices 116 detects a portion of the optical signal, converts the optical signal into an electrical signal (not shown) and communicates the electrical signal to circuitry 12. In this way, the clock signal 5 encoded onto optical signal 120 is very quickly distributed across the entire chip with minimal clock phase skew.

A variation of the optical distribution configuration of FIG. 2A is illustrated in FIG. 2B, showing a cross-sectional view of an integrated circuit chip 100B. Like integrated 10 circuit chip 100A of FIG. 2A, integrated circuit chip 100B includes substrate 13 and waveguide 110, but the electronic circuitry and electron tunneling device layers have been combined. A combination layer 130 includes circuitry 132 with electron tunneling devices 116 monolithically integrated thereon such that electron tunneling devices 116B are disposed alongside electrical components (not individually shown) in the circuitry layer. Electron tunneling devices 116B may be formed during the same fabrication steps as those used to form circuitry 132 or may be formed separately 20 following the fabrication of circuitry 132.

The optical clock distribution configurations shown in FIGS. 2A and 2B present an improvement over the conventional, electrical clock distribution schemes, in which clock signals are provided as electrical signal through electrical 25 lines that take up chip real estate, produce significant clock skew and produce electromagnetic pickup. The optical clock distribution configurations of FIGS. 2A and 2B avoid these problems inherent to electrical clock signals by taking advantage of the fact that the interconnect assembly of the 30 present invention, including the electron tunneling devices and waveguide, may be added on top of an existing integrated circuitry chip. It is often a difficult task in chip layout design to ensure that the clock signal reaches all parts of the chip simultaneously without degradation and while main- 35 taining a constant phase across the chip. Since optical signals in waveguides travel much more quickly and more directly than electrical signals in electrical lines, an optical clock signal may be distributed over the chip much more quickly than an electrical clock signal. The optical clock 40 signal broadcast into the waveguide layer may be picked up by the electron tunneling devices through, for instance, vias where needed.

Various modifications to the optical clock distribution configuration of FIGS. 2A and 2B are contemplated. One 45 such example is shown in FIGS. 3A and 3B. Like previously discussed embodiments of the present invention, an integrated circuit chip 150 shown in FIG. 3A includes circuitry 12 on top of a substrate 13. Like integrated circuit chip 100A of FIG. 2A, integrated circuit chip 150 also includes tun- 50 neling device layer 102. Integrated circuit chip 150 further includes a modified waveguide layer 152, which is designed to receive optical signal 120 carrying a clock signal 122 when the optical signal is incident normally on modified waveguide layer 152. A grating coupler 154, which is 55 integrated into modified waveguide layer 152, couples optical signal 120 into modified waveguide layer 152 such that optical signal 120 is radially broadcast throughout modified waveguide layer 152 as an optical clock signal (represented by arrows 156).

Details of modified waveguide layer 152 as well as tunneling device layer 102 are more readily apparent in FIG. 3B, which illustrates integrated circuit chip 150 in cross section. As shown in FIG. 3B, modified waveguide layer 152 includes grating coupler 154, which is designed to receive 65 optical signal 120 and to direct the optical signal so received throughout modified waveguide layer 152 as optical clock

20

signal 156. Optical clock signal 156 is picked up by electron tunneling devices 116 at desired points across the integrated circuit chip. Electron tunneling devices 116 then communicate the optical clock signal to electrical components in the circuitry wherever needed.

As in the case of integrated circuit chip 100A of FIG. 2A, the optical clock distribution scheme used in integrated circuit chip 150 is advantageous because the optical clock signal is distributed over the entire chip within picoseconds without being hampered by electrical delays. As a result, the clock signal received at the chip circuitry does not experience significant delay that may cause phase differences in different part of the chip. Also, since the optical clock signal is transmitted optically and is converted to an electrical signal by an electron tunneling device only where needed, electromagnetic pickup is reduced in comparison to conventional, electrical clock distribution through electrical transmission lines.

Various modifications to the optical clock distribution schemes shown in FIGS. 2A–2B and 3A–3B are possible. For example, the optical clock signal may be broadcast over the integrated circuit chip through free-space and subsequently picked up by the electron tunneling devices at various locations on the integrated circuit chip. Such a free-space transmission scheme may include, for instance, additional optical components such as lenses, holographic optical elements and filters. Other modifications may be apparent to those skilled in the art while remaining within the spirit of the present invention.

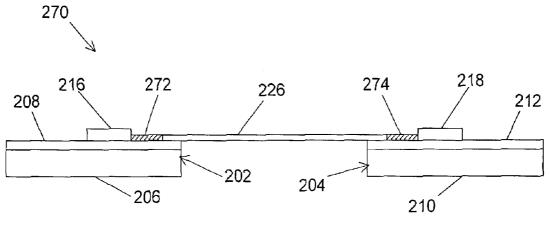

Turning now to FIGS. 4A and 4B, still other alternative embodiments of an interconnect assembly of the present invention using optical fibers are illustrated. FIG. 4A shows an interconnect assembly 200. Interconnect assembly 200 includes first and second chips 202 and 204, respectively. First chip 202 includes a substrate 206, on which circuitry 208 is formned. Similarly, second chip 204 includes a substrate 210 with circuitry 212 formed thereon. The first and second chips further include a first electron tunneling device 216 and a second electron tunneling device 218, respectively, formed thereon. In the embodiment as shown in FIG. 4A, first electron tunneling device 216 is configured to act as an emitter, such as those disclosed in the patent applications referenced above. First electron tunneling device 216 emits a light beam 220, which is focused by a first lens arrangement 222 onto an optical fiber input 224. Light beam 220 is then transmitted through an optical fiber 226 in the direction indicated by an arrow 228 toward an optical fiber output 230. At optical fiber output 230, light beam 220 is then focused by a second lens arrangement 232 onto second electron tunneling device 218. For instance, second electron tunneling device 218 may be an electron tunneling device, as disclosed in the P1 and P2 patents and P3, P3-cip and P1-cip applications, which is configured to act as a detector so as to receive light beam 220. Alternatively, a conventional detector, such as a silicon-based detector, may be used as second electron tunneling device 218. In this way, an optical interconnection is established between devices on first and second chips 202 and 204, thereby allowing transfer of data therebetween. Such an 60 optical interconnection is advantageous over, for example, electrical interconnections in terms of speed, signal loss, propagation distance and drive power.